# Welcome to

#### Conference

January 28–30, 2025 Santa Clara Convention Center Ехро

January 29–30, 2025

JAN. 28–30, 2025

#DesignCon

# Accelerating Time-to-Market in the Chiplet Era

Chiplet architecture and case study focusing on security and system protection

Junie Um, (Cadence) Samuel Wong, (Secure-IC)

JAN. 28–30, 2025

#DesignCon

### **SPEAKERS**

#### Junie Um

#### Distinguished Engineer, Compute Solutions Group/SSG, Cadence

Junie Um has been working on system and SoC architecture for a series of mobile and ADAS SoCs. Currently, she is responsible for chiplet and ADAS system architecture at Cadence. She received a BS degree from Seoul National University and MS and PhD degrees from the Korea Advanced Institute of Science and Technology (KAIST). She also served as a visiting scholar at the University of Texas at Austin.

#### **Samuel Wong**

#### Business Development Manager, Secure-IC

Sam Wong leads business development and sales activities for Secure-IC, bringing over 20 years of experience in international business development and semiconductor IP licensing. He began his career at Arm in Austin, focusing on emerging markets and managing the Arm Foundry Program. Sam then leads Tensilica's APAC sales operations, playing a pivotal role in opening the China and Taiwan markets. He also serves in various roles at Boeing, NetSpeed, and an Al startup.

#DesignCor

JAN. 28-30, 2025

informa markets

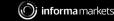

# The Journey of a SoC designer

- Heterogenous SoCs

- Single, monolithic die

- Integration of IP with some specialized IP

- Designers look for ways to build bigger, faster, and cheaper systems

- Multi-die solutions to build big

- 。 Multi-chiplet solutions to build faster and cheaper with more specialization

Monolithic Die

Heterogeneous Chiplet System

**Extreme Specialization**

#DesignCon

JAN. 28-30, 2025

informa markets

# Why Chiplets? An Engineering Value Proposition

- 1. Cost-effectiveness and complexity efficiency

- Focus engineering teams on unique value-add while improving time to market, project derisk, and costs

- Leverage partners for advanced-node designs, IP, and software virtual platform

- 2. Modularity Scalability and customizations

- Enabling very large systems *make it big* multi-chip solutions

- Scalable solutions from low- to high-end make it fast, make it cheap multi-chiplet solutions

- 3. Portfolio management

- Develop product roadmaps built with the same chiplets

- Reuse of select chiplets for next-generation products

- 4. Ecosystem development

- Leverage software ecosystem around partner chiplets (reference design)

#DesignCon

Utilize off-the-shelf chiplets (standard IP – CPU, GPU, memory, I/O)

JAN. 28-30, 2025

# **Cadence Chiplet Development Efforts**

- Reference designs to accelerate the design effort

- Base System Chiplet Tapeout completed in October 2024

- Building NPU chiplet targeting Q3 2025

- Continue to build a reference platform

- Supporting configurable subsystem

- Chiplet frameworks to simplify chiplet construction

- Building SoC cockpit to accelerate the design effort

- Designing to support the standard chiplet system architectures

- Joining standardization efforts

- How chiplets interoperate the behavior of chiplets

- How chiplets communicate data/event communication of chiplets

#DesignCon

JAN. 28–30, 2025

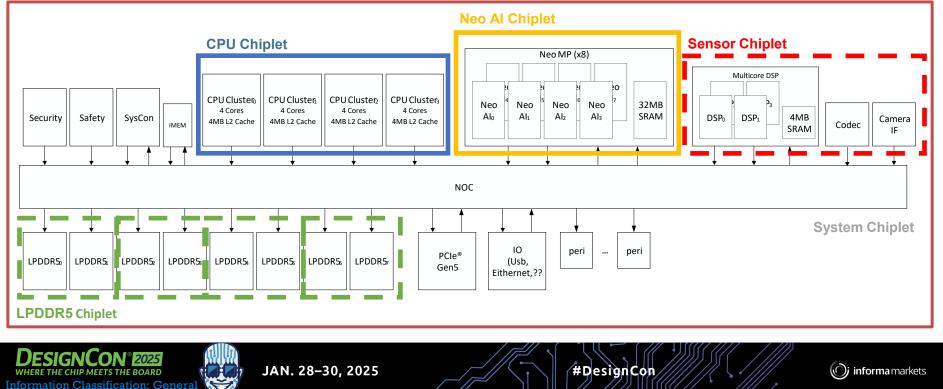

# **Example ADAS Chiplet Decomposition**

- CPU, Cadence<sup>®</sup> Neo<sup>™</sup> AI, system functions with optional sensor, memory, and I/O chiplets

- Tradeoff process cost, yield, performance, package cost, scalability, extensibility

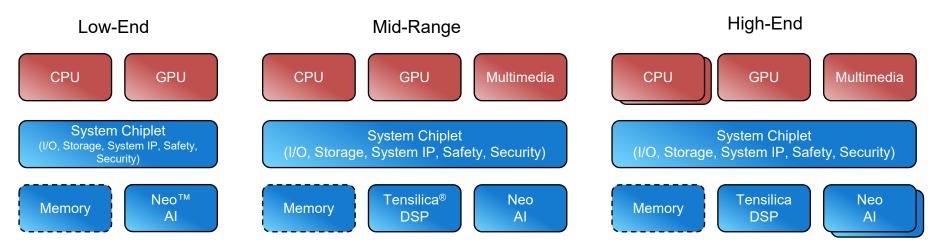

# **ADAS Product Family with Chiplets**

Great example for configurable and scalable systems

#DesignCon

- Architect a set of chiplets to build a range of solutions

- Ability to upgrade portions of the system

- Common architecture and software environment across all vehicles

- <sup>o</sup> Software verification is among the greatest challenges for automotive OEMs

JAN. 28-30, 2025

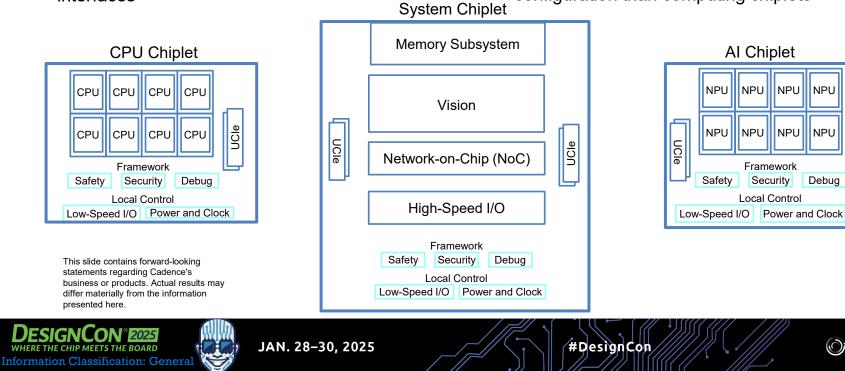

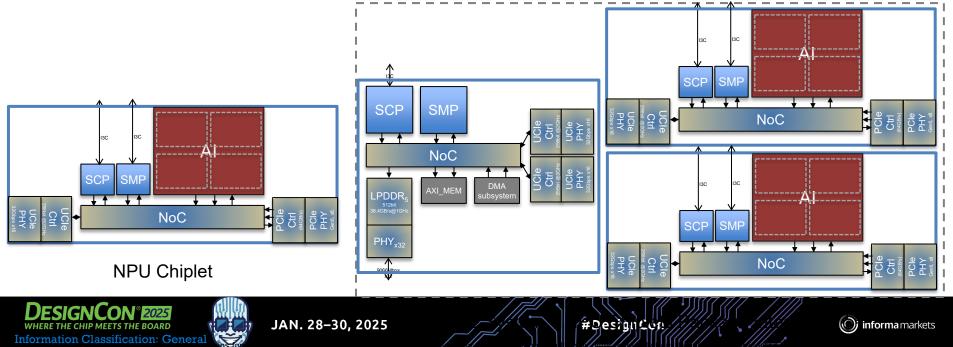

### Reference Platform

- Initial version will run at 1H'25 in emulation

- SoC-level control functionality for the security, safety, and control subsystems distributed over multiple chiplets, connected via UCIe<sup>™</sup>, I3C, and event interfaces

- Chiplet framework encapsulates the subsystem into chiplet and provides cohesive communication between the chiplets

NPU

Debua

(informa markets

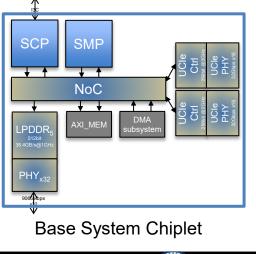

Base system chiplet supports a more flexible configuration than computing chiplets

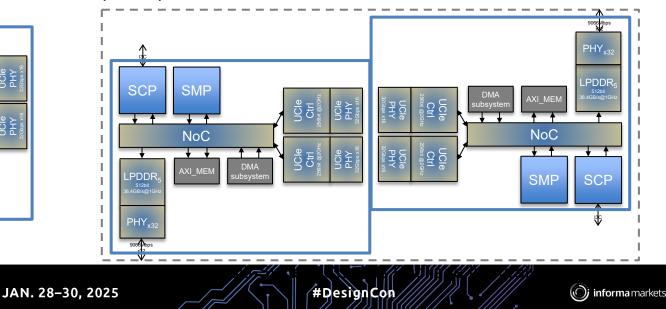

# **Base System Chiplet (Tapeout Completed Oct 2024)**

Advanced-node base system chiplet with system processor and LP5

Information Classification: General

Each base system chiplet contains: UCle<sup>™</sup> PHY and Controller, chiplet, system control processor (SCP), safety management processor (SMP), root of trust (ROT), LPDDR5, and NoC

# **NPU Chiplet**

NPU chiplet with multicore NPU Each NPU chiplet contains UCIe<sup>™</sup> PHY and Controller, system control processor (SCP), safety management processor (SMP) ROT (Root of Trust), multi-core NPU, PCIe<sup>™</sup> PHY and controller, and NoC technology

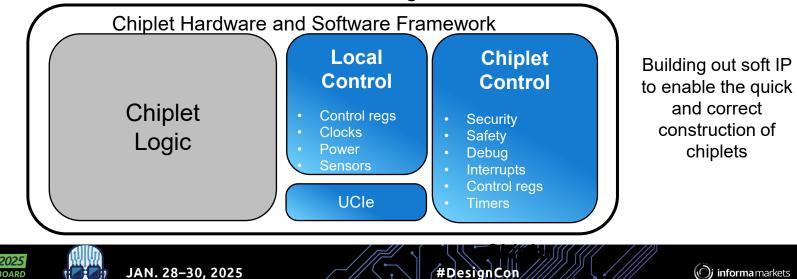

# **Supporting Chiplet Architectures**

**Chiplet frameworks**

Information Classification: General

- Supporting chip-to-chip behavior across chiplets

- ₀ Memory interface based on UCIe<sup>™</sup> IP

- Security/safety/control interface based on events and I3C interfaces

- Spec-based framework to accelerate the design effort

# Inter-Chip Management in System in Package

(informa markets

#DesignCon

Define interoperable behavior interoperable interfaces between the chiplet

- Behavior define

- Secure Boot (System-in-Package)

- System Protection

- Safety Control (Autonomous Application only)

- System Control

- Data Communication

- System Synchronization

- System Debug

- Mapping the data/event exchange into interchip interfaces

- 。 UCIe<sup>™</sup> interface, (mainband and sideband)

- Event interface

- Signal interface

JAN. 28–30, 2025

#### STRATEGIC ANNOUNCEMENT

SECURE-IC IS EXPECTED TO BECOME THE SECURITY ENTITY IN CADENCE DESIGN SYSTEMS

# cādence ×

#### A GLOBAL LEADER IN EMBEDDED SECURITY

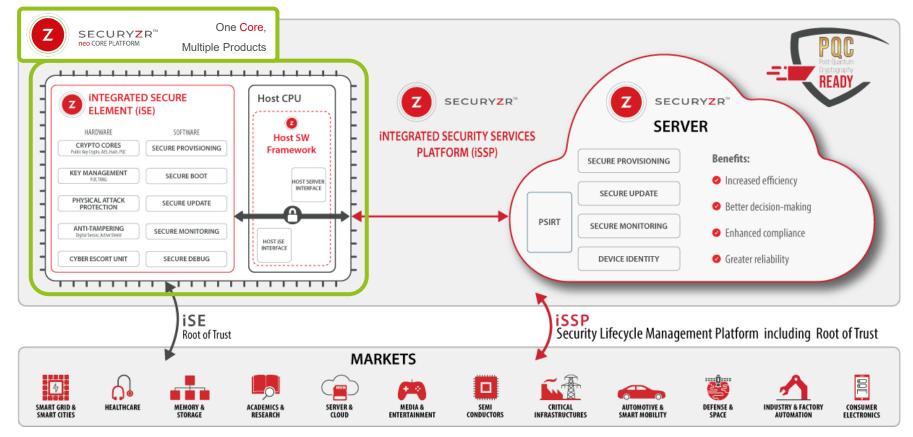

IoT devices being interconnected, **each and every object could be a threat for the whole network.**

Therefore, the security of the objects or the devices with their

**lifecycle management is key**, and so is their data. To ensure the integrity of this data, the whole system must be secured and managed. **Trusted devices enable trusted data**. ONE DAY, SECURITY WILL BE WORTH MORE THAN THE DEVICES

Secure-IC partners with its clients to provide them with the best end-to-end cybersecurity solutions for embedded systems and connected objects, **from Chip to Cloud**

#### THE RISING LEADER IN THE SECURITY INDUSTRY

Down to 18A/2 N

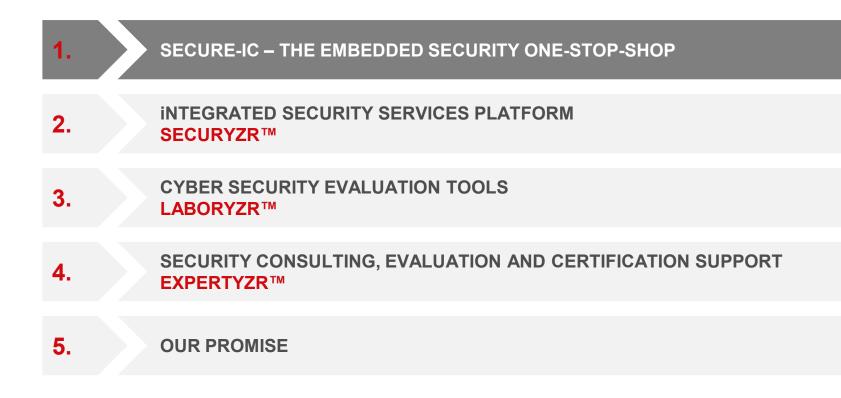

E S ONE-STOP-SHOP for embedded security

> 250+ patents

MULTI-CERTIFIABLE technologies for multiple markets

Unique & patented technologies: ANTI-TAMPER & CYBER-PHYSICAL attack protection \*\*\*

> PQC and Al-POWERED SECURITY

FULLY DIGITAL technology for all technology nodes and foundries

Management of security ALL ALONG DEVICES' LIFECYCLE

MATURE & WIDELY DEPLOYED solutions

350+ publication

S

10+

years

#### NUMEROUS MARKETS FOR EMBEDDED SECURITY

#### Automotive

#### Mobile / High Security

#### Edge / AI / OT

#### Networking / Server

ΙοΤ

#### **Additional Markets**

#### THE ROOT OF TRUST APPROACH

#### SUPPORT FOR ALL CHALLENGES FROM SECURITY REQUIREMENTS TO SECURITY MANAGEMENT ALONG THE LIFECYCLE OF SYSTEMS

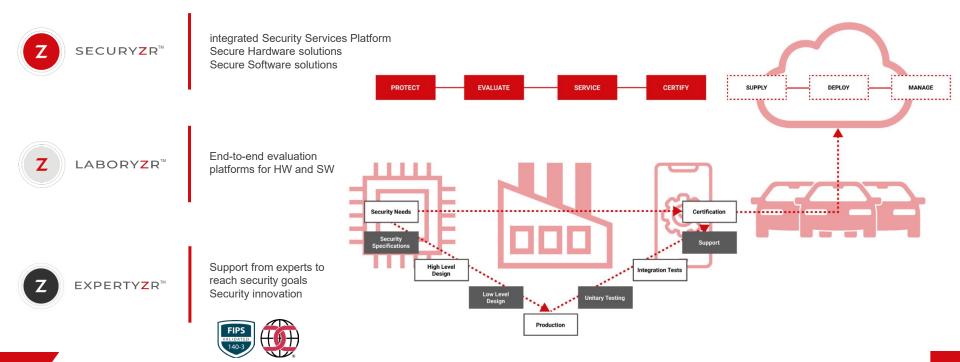

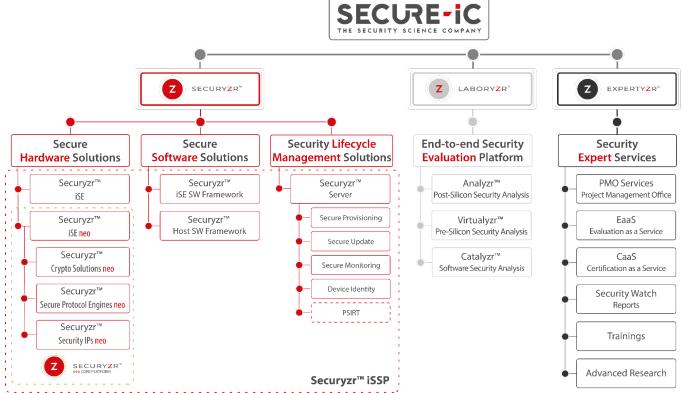

#### A COMPLETE SET OF END-TO-END SECURITY SOLUTIONS

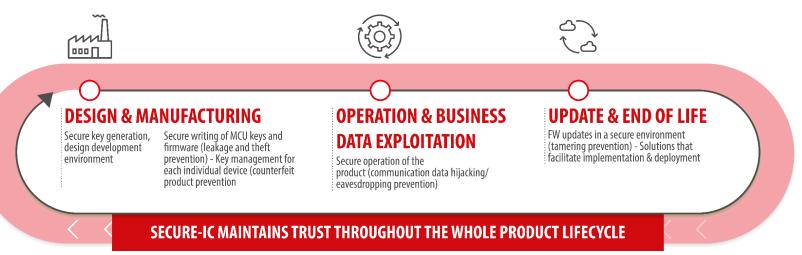

# YOUR END-TO-END PARTNER FOR SECURITY ALL ALONG THE DEVICE LIFECYCLE

While globalized sourcing and manufacturing processes reduce costs, they increase risks exposure. Considering the complexity of value chains, the challenge is to generate and manage trust in data.

### Secure-IC aims at answering this challenge relying on interoperability and open standards.

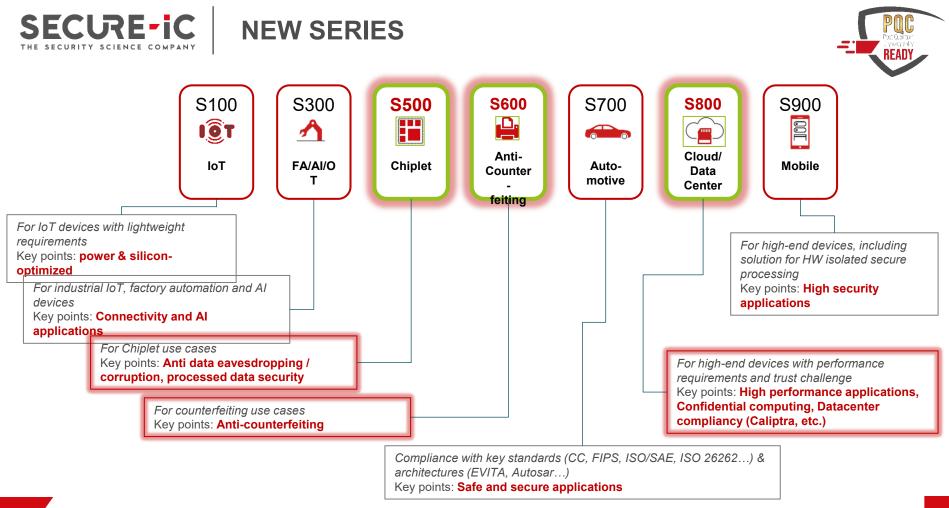

#### **EMBEDDED SECURITY FOR ALL YOUR NEEDS**

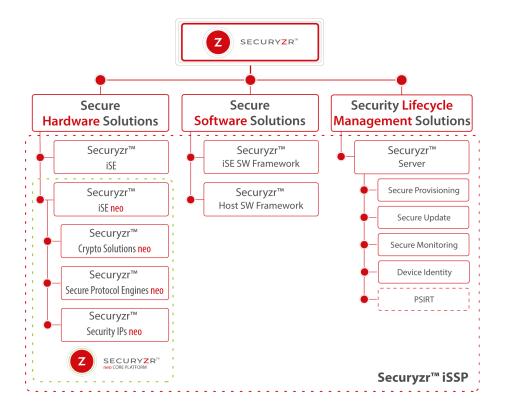

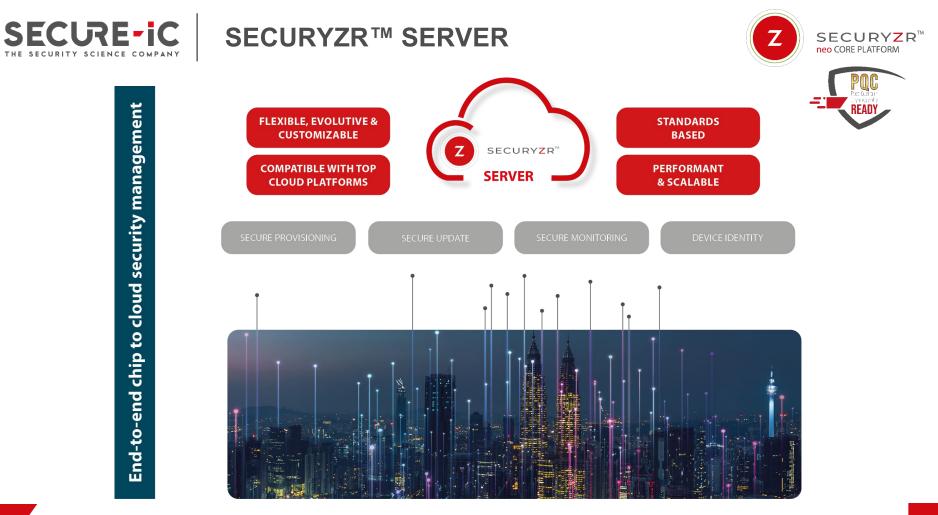

■ Securyzr<sup>™</sup> neo Core Platform

- One core, multiple products

- Post-Quantum Cryptography (PQC) ready

- ASIC & FPGA compatible

- Technology node down to <u>2nm</u>

- Trustful zero-touch security server solution

- Al powered

World Class Standards

#### SECURYZR<sup>™</sup> neo CORE PLATFORM

#### Benefit From Secure-IC's Rich Legacy while Embracing Cutting-edge Technologies

#### SECURYZR™ iSSP SOLUTION MAINTAIN TRUST THROUGHOUT THE WHOLE DEVICE LIFECYCLE

**SECURE-IC / CADENCE CHIPLET PROJECT**

#### ADAS chiplet platform – a first successful project

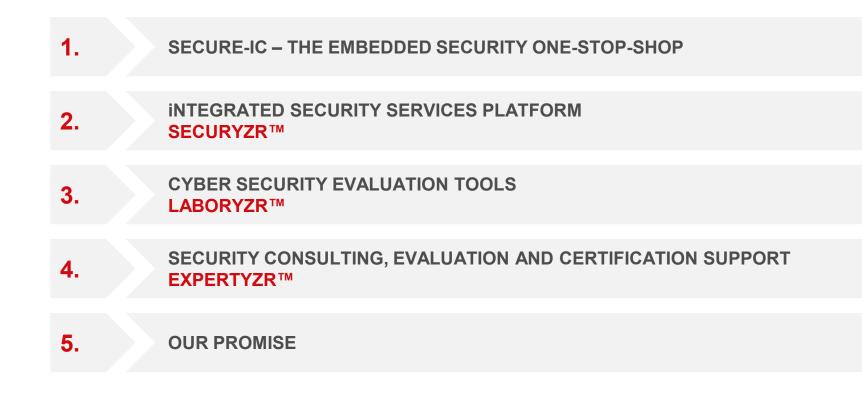

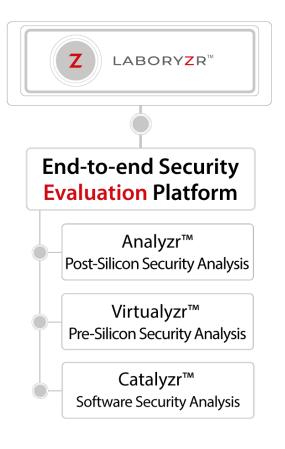

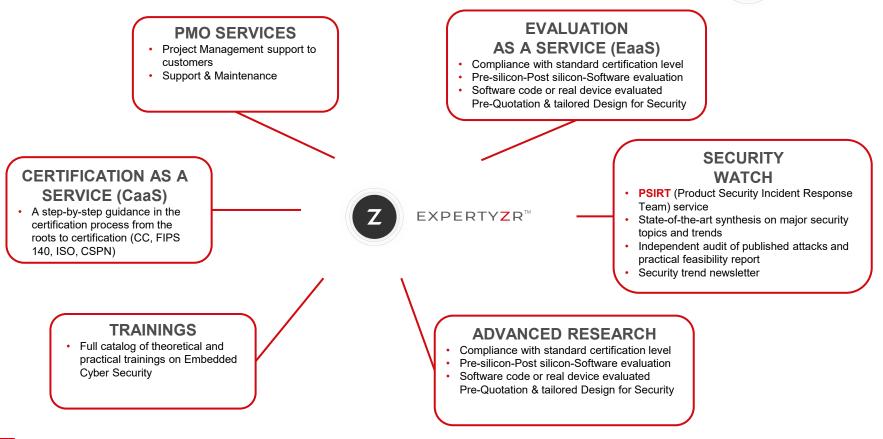

#### **CYBERSECURITY EVALUATION TOOLS**

- From Pre-Silicon to Post-Silicon

- Side Channel & Fault Injection Analysis / Attacks

- Reverse Engineering

- Hardware Trojan detection

- Standard certifications compliance

- Common Criteria

- FIPS-140

- OSCCA

- ISO 17825/20085

- And more...

#### **SERVICE & CERTIFY**

- Security services

- Risk assessment

- White / Grey / Black Box analysis

- Standards & Certifications compliance check and support

- Cyber Threat Intelligence

- Cybersecurity awareness

PSIRT

#### A COMPLETE SET OF EXPERTS' SERVICES

THE SECURITY SCIENCE FACTORY THOUGHT LEADERSHIP

- SCIENTIFIC WORK AND PUBLICATIONS

- More than 350 published papers

- 250+ patents

- SECURITY THOUGHT LEADERSHIP

- 40+ presentations per year in Semiconductor and Embedded security events

#### STANDARDIZATION

- Equipment for non-invasive attacks: ISO/IEC 20085

- Physically Unclonable Functions: ISO/IEC 20897

- White-Box Cryptography: SC27/WG3 N1367

- Connected Car Cybersecurity: ISO/SAE 21434

- Autonomous Vehicle Working Group 3 (AVWG 3) Cyber Security

- Information security, cybersecurity and privacy protection: ISO/IEC CD TR 5891 - Hardware monitoring technology for hardware security assessment

- Side-channel leakage of cryptographic implementations assessment: ISO/IEC 17825

**OUR PROMISE** CREATE TRUST FROM CHIP-TO-CLOUD

- Secure-IC is a <u>trust enabler</u>, thanks to its unique positioning as a onestop-shop security partner

- Protection from Edge Device chips to Cloud, along their <u>lifecycle</u>

- PQC is the next revolution and Secure-IC is a pioneer in the field

- Root of Trust, security in depth by design

# Thank you!

### **QUESTIONS?**

#### Sam Wong

Director US Sales, Secure-IC Samuel.wong@secure-ic.com | www.secure-ic.com

#DesignCon

() informa market

Property of

JAN. 28–30, 2025

# cādence

© 2025 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.