# Welcome to

#### Conference

January 28–30, 2025 Santa Clara Convention Center Ехро

January 29–30, 2025

JAN. 28–30, 2025

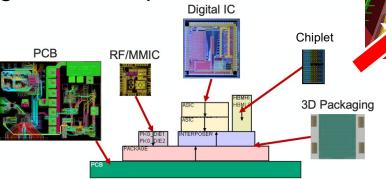

# The Role of EDA as Chips Transform Into 3D Systems

John Park, Cadence

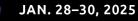

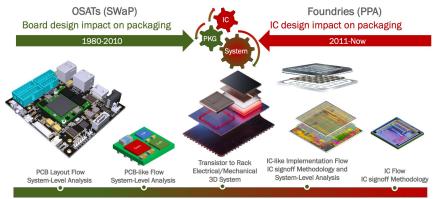

### For ASIC Designers, Simply Following Moore's Law Alone Is No Longer the Best Technical and Economical Path Forward

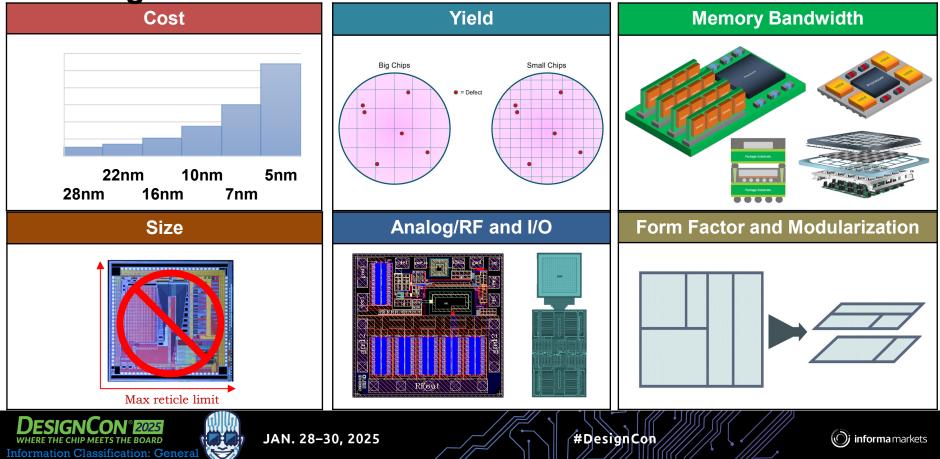

### Technology Breakthroughs in Semiconductor Packaging is Key to Transforming Chips Into 3D Systems

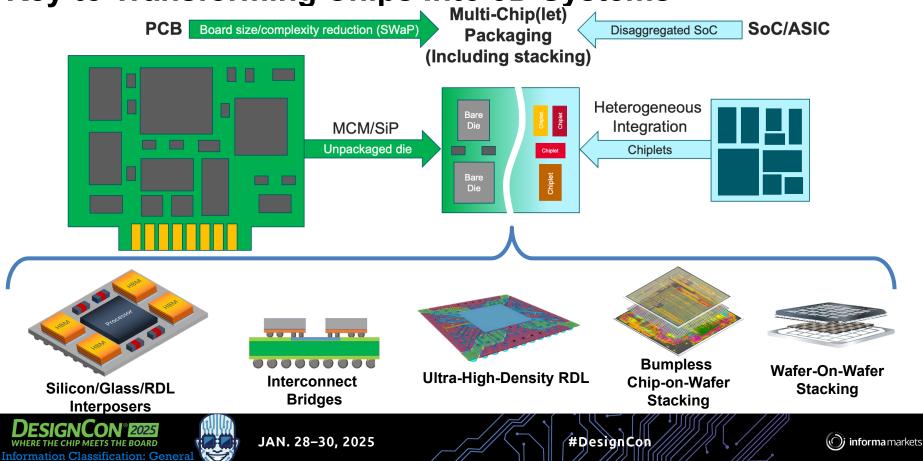

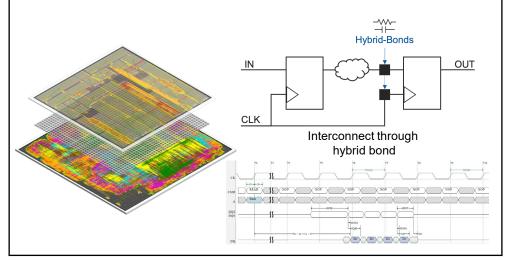

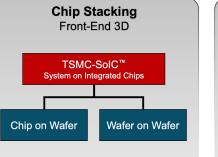

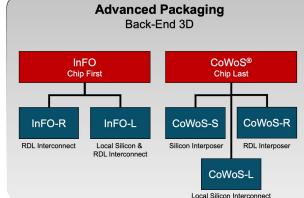

## 3D Packaging vs Chip/Wafer Stacking (3DHI)

#### **3D Packaging**

- Solder-based connections (35-150um)

- Dies designed independently

Black-box modeling

- I/O buffer-to-buffer signaling

#### **Chip/Wafer 3D Stacking**

- Solder-free connections (<10um)</li>

- Single RTL partitioned at implementation

Full detail of IC required for layout

- DBI, hybrid-bond, cu-to-cu, and direct connection

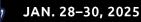

#### The Wild West of Semiconductor Packaging

100s of ways to package devices

JAN. 28–30, 2025

### **Design and Analysis Challenges**

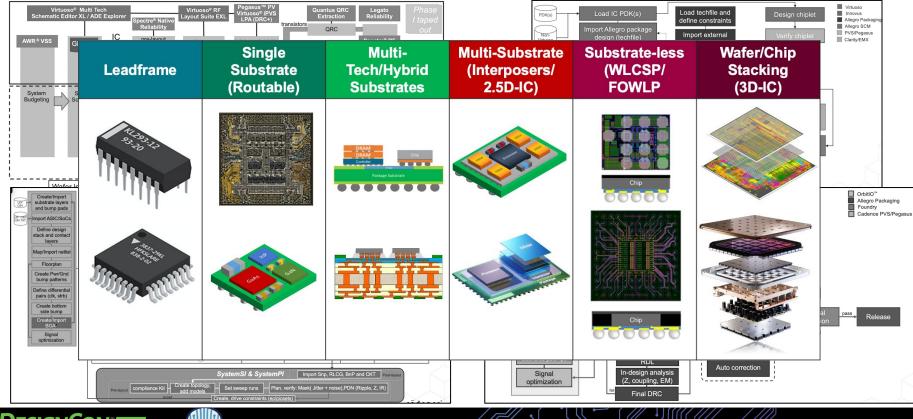

#### **Complex Design Flows**

- Convergence of systems and ICs driving an explosion in the number of design tools and leads to complex design flows

- Mechanical tools will be next to come

- Co-design/co-analysis across die/chiplet/package

- Support for existing and emerging 3D-IC standards

- Layout stage too late for electrical and thermal analysis

- All tools need to be three-dimensional system-aware

Complex 3D floorplans

#### Implementation and Signoff

- Lack of design manufacturing and assembly data

- Assembly design kits (ADK) are lacking

- $_{\circ}$  Single source of truth

- Laminate design vs. silicon design

- Advanced IC-style design rules

- 。 SystemLVS

- Mechanical engineering tasks (warpage, cold plates, etc.)

- D2D and D2S routing bottlenecks

#DesignCon

JAN. 28–30, 2025

informa markets

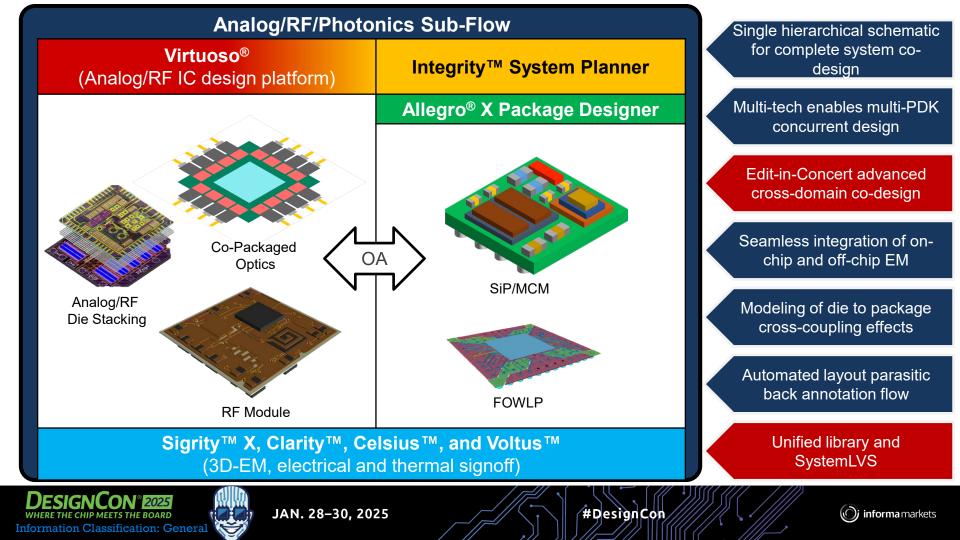

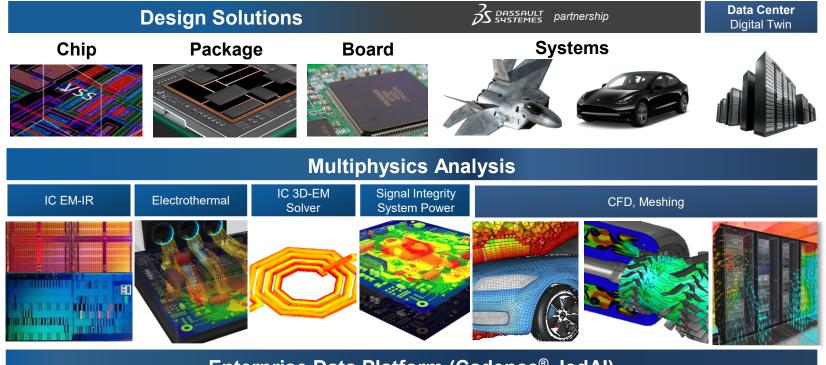

### Digital/Analog/RFIC, SiP/MCM, PCB, and System Analysis

| IC Design                                     | Simulation                                                         | SiP/MO                               | SiP/MCM and PCB                                                                          |           | Analysis                                                              |  |

|-----------------------------------------------|--------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------|--|

| Innovus™, Virtuoso®, and<br>Microwave Office® | Spectre <sup>®</sup> , Legato <sup>™</sup><br>Xcelium <sup>™</sup> |                                      | Allegro <sup>®</sup> X, OrCAD <sup>®</sup><br>PSpice <sup>®</sup> , InspectAR, and Pulse |           | sius <sup>™</sup> , EMX®<br>s <sup>™</sup> , and Sigrity <sup>™</sup> |  |

| Advanced node/ML automation                   | Digital logic verificat                                            | ion Higl                             | High-speed PCB                                                                           |           | ctromagnetics                                                         |  |

| Digital, analog, RF, and photonics            | Reliability                                                        | Advanc                               | Advanced IC packaging                                                                    |           | thermal                                                               |  |

| MMIC                                          | RF and AMS simula                                                  | tion Augmente                        | Augmented reality and ML/AI                                                              |           | Computational Fluid Dynamics                                          |  |

| Cadence.Al – C                                | Cadence <sup>®</sup> Joint Ent<br>Generative                       | cerprise Data and<br>Al Applications | AI (JedAI) Pla                                                                           | tform     |                                                                       |  |

| Digital<br>Design                             | Analog/Custom<br>Design                                            | Debug and<br>Verification            |                                                                                          |           | ltiphysics<br>timization                                              |  |

|                                               | Ecosystem C                                                        | ollaboration and Pa                  | rtnerships                                                                               |           |                                                                       |  |

|                                               | ptimized Customer and                                              | d Cadenced Manag                     | ed Cloud-Based S                                                                         | Solutions |                                                                       |  |

|                                               |                                                                    |                                      |                                                                                          |           |                                                                       |  |

, //

Information Classification: General

WHERE THE CHIP MEETS THE BOARD

JAN. 28–30, 2025

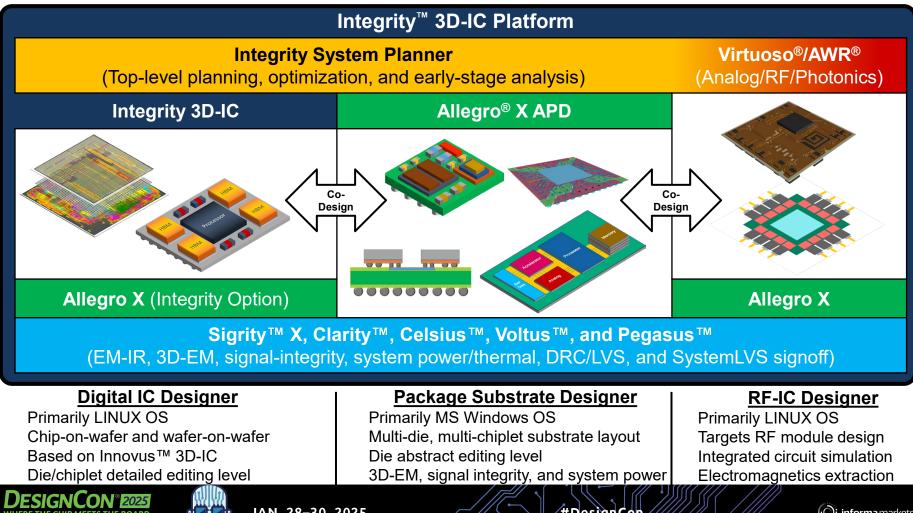

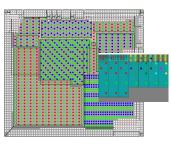

#### **Integrity System Planner** 3D system-level aggregation and optimization

Chip(let)-chip(let)-package-board signal-mapping

Early-Stage Power/Thermal/SI Analysis

WHERE THE CHIP MEETS THE BOARD Information Classification: General

Hierarchical Planning and Optimization of System-Level Design and Connectivity

3Dblox<sup>™</sup> & 3DCODE Support

Advanced bump/TSV/TDV planning

SystemLVS (Rule-Deck-Free)

### **Cadence Capabilities Enabling Electronic Product Realization**

| -                                                                                                                                                                                                   |                                                                                                                           |                                                                                      |                                                                                                                           |                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| EDA Design Tools                                                                                                                                                                                    | Reference Design<br>Flows                                                                                                 | Design IP/Chiplets                                                                   | Design Services                                                                                                           | Government<br>Programs                                                                                                 |

| <ul> <li>Digital IC</li> <li>Analog/RF IC</li> <li>Advanced Packaging</li> <li>3D-IC</li> <li>PCB</li> <li>MMIC</li> <li>Thermal</li> <li>Power</li> </ul>                                          | <ul> <li>3DHI</li> <li>RF-IC</li> <li>Digital ASIC</li> <li>System analysis</li> <li>Partner software overlays</li> </ul> | <ul> <li>D2D (UCle)</li> <li>DIP</li> <li>TIP</li> <li>Security</li> <li></li> </ul> | <ul> <li>ITAR Compliant</li> <li>Digital ASIC</li> <li>3DHI</li> <li>RF module</li> <li></li> </ul>                       | <ul> <li>DARPA CHIPS</li> <li>RAMP/RAMP-C</li> <li>ERI</li> <li>SHIP</li> <li>NGMM</li> <li>NAPMP</li> <li></li> </ul> |

| <ul> <li>Signal Integrity</li> <li>3D Electromagnetics</li> <li>CFD</li> </ul>                                                                                                                      | 。 Cloud                                                                                                                   | Emulation                                                                            | Assembly Design<br>Kits                                                                                                   |                                                                                                                        |

| <ul> <li>Functional<br/>Verification</li> <li>STA</li> <li>Physical Verification</li> <li>System Planning</li> <li>Reliability</li> <li>Data Management</li> <li>3D Mechanical</li> <li></li> </ul> | <ul> <li>On-Prem</li> <li>Hybrid</li> <li>Secure Gov</li> <li></li> </ul>                                                 | <ul> <li>ASIC</li> <li>FPGA</li> <li>Digital Twinning</li> <li></li> </ul>           | <ul> <li>PDK for 3DHI</li> <li>ADK Automation</li> <li>ADK<br/>Collaboration</li> <li>All stages of<br/>design</li> </ul> |                                                                                                                        |

| DESIGNCON® 2025<br>WHERE THE CHIP MEETS THE BOARD                                                                                                                                                   | JAN. 28–30, 2025                                                                                                          |                                                                                      | #DesignCon                                                                                                                | informa markets                                                                                                        |

Information Classification: General

#### **Cadence Assembly Design Kit (ADK)**

| TechFiles                                 | Design Libraries                                   | <section-header></section-header>                                                |                                                                          | Manufacturing Rules                                             |                                                       |

|-------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|

| Layer stack-up<br>Material<br>Properties  | Footprints and<br>Power/Thermal models<br>Chiplets | Device placement<br>constraints based<br>on assembly pick and<br>place equipment | Electrical spec<br>validation of<br>chip(let)-to-chip(let)<br>interfaces | Board/substrate<br>manufacturing<br>process<br>Substrate checks | Foundry/<br>semiconductor<br>manufacturing<br>process |

| Thickness                                 | Discrete                                           | Device to device spacing                                                         | Interconnect library                                                     |                                                                 | DRC                                                   |

| Physical/Electrical<br>layout constraints | BGA/LGA/Interposer                                 | Device to obstacle                                                               | I/O libraries                                                            | Soldermask checks                                               | LVS                                                   |

| Line and space                            | Via structures                                     | Device to edge                                                                   | Eye masks                                                                | Silkscreen checks                                               | SystemLVS                                             |

| Differential signaling                    | D2D routing topologies                             | Max stack height                                                                 | Jitter tolerance                                                         |                                                                 | Metal fill                                            |

| Customized in-design<br>DRCs              | STEP Models                                        |                                                                                  | Insertion/return loss                                                    | Tech file compare                                               |                                                       |

| RAVEL                                     | Library compare                                    |                                                                                  |                                                                          |                                                                 |                                                       |

| Design templates                          |                                                    |                                                                                  |                                                                          |                                                                 |                                                       |

### **Benefits of an Assembly Design Kit**

#### Benefits of an ADK

Bounds the packaging challenge for highvolume design manufacturing

Creates a more seamless interaction between endcustomer and OSAT/Foundry

Provide collateral necessary to run all tools in supported flows, enabling consistency across users

Single source of truth for multi-chip packaging

Organize data so that users don't have to guess at tool setups

Prevent manual entry/error by users of critical foundry data (line spacing, vias, etc.)

Supports private and public repositories

Creates self-contained workspaces and manages versions and ECOs

An ADK is specific to a particular CAD tool/flow

#### DESIGNCON® 2025 WHERE THE CHIP MEETS THE BOARD Information Classification: Gene

#### What an ADK is NOT

Cadence helps companies build ADKs, we don't provide ADKs

ADKs are not a design/layout service

#DesignCon

For single-use case

There is no industry standard for an ADK

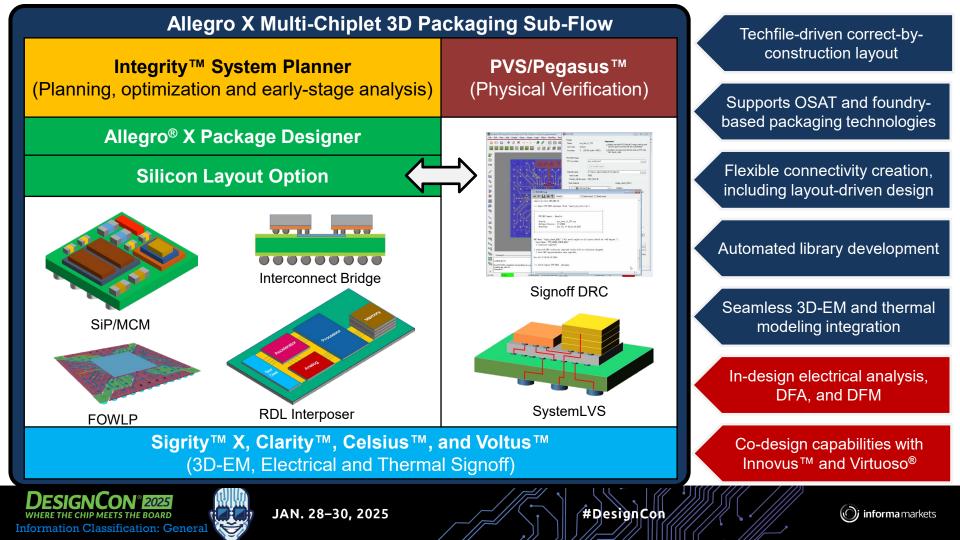

### Cadence Has Tools/Flows to Support All Multi-Die, Multi-Chiplet 3D-HI Packaging

| Package Type            | Integrity™<br>3D-IC<br>Platform | Virtuoso®<br>Studio<br>(VMT) | Allegro® X<br>Silicon<br>Layout<br>Option | PVS/<br>Pegasus™<br>(DRC/LVS) | Sigrity™/Clarity<br>™<br>(3D-EM, System<br>Power, and SI) | Voltus™<br>Fi<br>(Die-<br>Level<br>EMIR) | Celsius™<br>(Thermal) | EMX®<br>(Die-Level<br>EM) |

|-------------------------|---------------------------------|------------------------------|-------------------------------------------|-------------------------------|-----------------------------------------------------------|------------------------------------------|-----------------------|---------------------------|

| Wirebond BGA            |                                 |                              | $\checkmark$                              |                               | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| FC BGA/LGA              |                                 |                              | $\checkmark$                              |                               | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| LTCC                    |                                 |                              | $\checkmark$                              |                               | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| FOWLP                   |                                 |                              | $\checkmark$                              | $\checkmark$                  | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| Interconnect<br>Bridges | ✓ <sup>B</sup>                  | ✓ <sup>B</sup>               | √s                                        |                               | √s                                                        |                                          | $\checkmark$          |                           |

| RDL Interposer          |                                 |                              | $\checkmark$                              | $\checkmark$                  | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| Silicon Interposer      | $\checkmark$                    | $\checkmark$                 |                                           | $\checkmark$                  | $\checkmark$                                              | $\checkmark$                             | $\checkmark$          | $\checkmark$              |

| Glass Interposer        |                                 |                              | $\checkmark$                              | $\checkmark$                  | $\checkmark$                                              |                                          | $\checkmark$          |                           |

| Bumped Stack            | $\checkmark$                    | $\checkmark$                 | $\checkmark$                              | $\checkmark$                  | $\checkmark$                                              | $\checkmark$                             | $\checkmark$          | $\checkmark$              |

| Bumpless Stack          | $\checkmark$                    | $\checkmark$                 |                                           | √                             |                                                           | $\checkmark$                             | √<br>///)             | $\checkmark$              |

JAN. 28–30, 2025

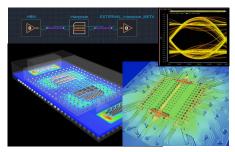

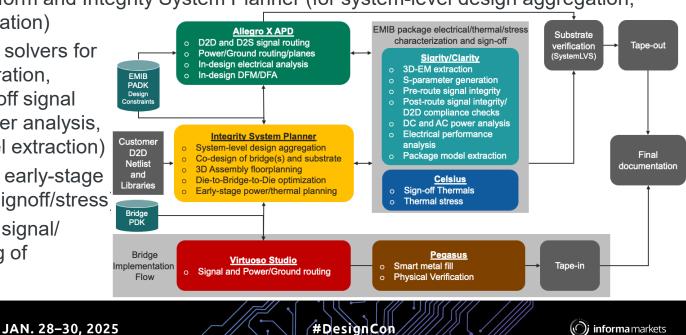

### Cadence and Intel Foundry Collaborate to Enable Multi-Chip(let) Design with EMIB Packaging Technology

- Joint effort has resulted in an advanced packaging flow:

- Cadence's Allegro<sup>®</sup> X APD (for placement, signal/power/ground routing, in-design electrical analysis, DFM/DFA and final manufacturing output)

- Integrity<sup>™</sup> 3D-IC Platform and Integrity System Planner (for system-level design aggregation, planning and optimization)

- Sigrity<sup>™</sup> and Clarity<sup>™</sup> solvers for two-parameter generation, early-stage and signoff signal integrity, DC/AC power analysis, and packaging model extraction)

- o Celsius<sup>™</sup> solvers (for early-stage) and signoff thermal signoff/stress

- Virtuoso<sup>®</sup> Studio (for signal/ power/ground routing of EMIB bridges)

Information Classification: General

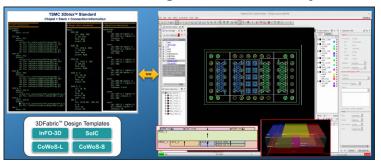

## **Reference Flows for TSMC 3DFabric<sup>™</sup> Wafer-Level System**

#### **Integration Technologies**

Cadence Tools Currently Certified for TSMC 3DFabric™ Flows

| Function        | Tools                        |           | Function   | Tools                        |  |

|-----------------|------------------------------|-----------|------------|------------------------------|--|

| Top-Level       | Integrity™ System            |           |            | Quantus™                     |  |

| Management      | Planner                      | Modeling/ | Extraction | Sigrity™ XtractlM™           |  |

|                 | Innovus™                     |           |            | Clarity™                     |  |

| Physical Design |                              |           |            | Tempus™                      |  |

|                 | Virtuoso®                    |           |            | Voltus™                      |  |

|                 | Allegro <sup>®</sup> X       |           | Analysis   | Sigrity SystemSI             |  |

| Verification    | Pegasus™-DRC<br>Pegasus™-LVS |           |            | Sigrity PowerSI <sup>®</sup> |  |

|                 |                              |           |            | Celsius™                     |  |

JAN. 28-30, 2025

#### **Cadence Transforms Chip Through Systems**

Enterprise Data Platform (Cadence<sup>®</sup> JedAl)

JAN. 28–30, 2025

# Thank you!

#### **QUESTIONS?**

#### John Park

Product Management Group Director, Cadence jpark@cadence.com | Cadence.com

#DesignCon

21