# Welcome to

#### Conference

January 28–30, 2025 Santa Clara Convention Center Ехро

January 29–30, 2025

JAN. 28–30, 2025

# Accelerate Silicon Interposer Development with Integrated Design and Analysis – A Cadence Exclusive

Pedro El Awar, Cadence

## Agenda

Problem Statement: Growing Complexity – Ultra-high-end packaging technologies being pushed to their limits

#DesignCon

(); informa markets

- Algorithmic Selective Cutting Methodology Proposition

- o Design platforms (Allegro<sup>®</sup> X PCB, Allegro X Advanced Package Designer)

- Simulation domain (In-design analysis, Sigrity<sup>™</sup> SI/PI, Clarity<sup>™</sup> 3D Solver)

- Algorithmic Selective Layout Cutting

- o What it is

- How it benefits design and simulation

- o Benchmarks

- Intelligent Multi-Block Extraction

- o Motivation, what it is

- How it benefits analysis

- Applications of the Intelligent Selective Cutting Methodology

- o Al-driven design synthesis with constraints

- o System-level SI post-route optimization methodology

- $\circ$  PDN analysis

- $\circ$  Heterogeneous system extractions

- Conclusion and Next Steps

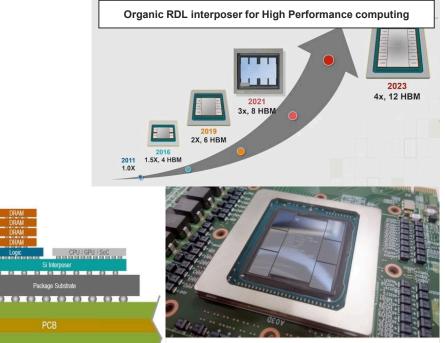

## **Problem Statement**

Growing complexity – Ultra-high-end packaging technologies being pushed to their limits

- In recent years, high-performance computing chip designs are pushing ultra-high-end packaging technologies to their limits

- Translators and layout tools cannot scale linearly to address the growing scale of engineering designs

- Need to provide customers the ability to distribute the layout and analysis efficiently within scalable workflows

- <u>Parallelization</u>, <u>integration</u>, and <u>Turn-Around-</u> <u>Time (TAT)</u> are keys to success

- Need to better integrate the layout of interposers, IC packages, and PCBs within the simulation and analysis domain (multi-fabric analysis)

- More extractions needed and earlier in the design cycle

https://www.anandtech.com/Show/Index/16036?cPage=3&a II=False&sort=0&page=1&slug=2023-interposers-tsmchints-at-2000mm2-12x-hbm-in-one-package

## Algorithmic Selective Cutting Methodology Proposition

### Design platforms (Allegro X PCB and Packaging)

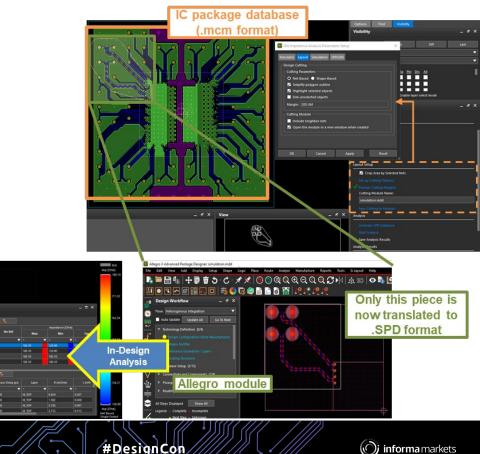

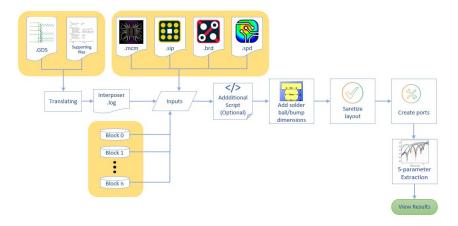

- Layout databases (.sip, .mcm) need to be translated to the Sigrity<sup>™</sup> file (.spd) format for extraction.

- Large designs or databases with many degassing holes or challenging geometries can take hours to be translated.

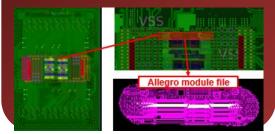

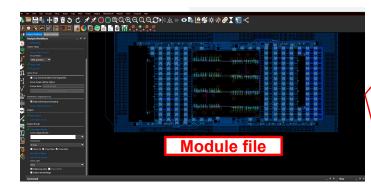

- <u>Algorithmic Selective Cutting:</u> Allegro<sup>®</sup> X and Allegro X Package Designer enhancements that enable the partitioning and stitching together of a layout design.

- Design will be cropped per user selected nets/margin, then translated.

- Reduces the <u>translation time</u> and accelerates the <u>SIPI extraction setup and overall runtime</u> to get results.

- Creates module files that can be shared across different teams (layout designers, SIPI engineers) and optimized and reapplied at the master design level.

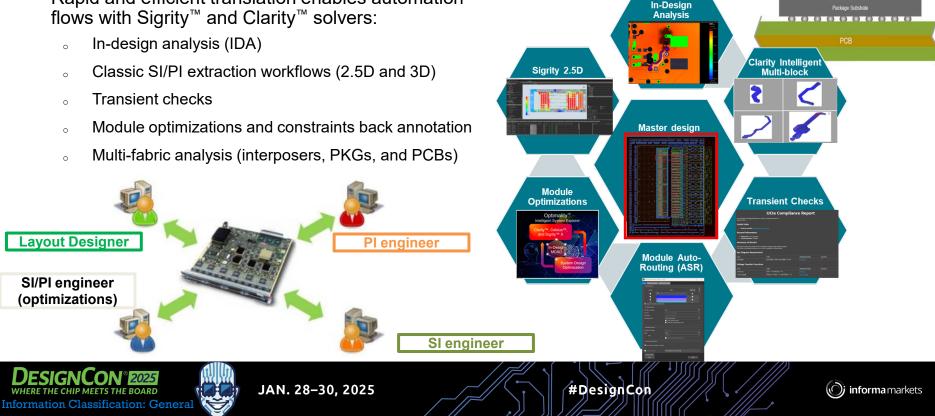

## Algorithmic Selective Cutting Methodology

### Analysis, Sigrity technology, Clarity 3D Solver

Rapid and efficient translation enables automation flows with Sigrity<sup>™</sup> and Clarity<sup>™</sup> solvers:

## **Algorithmic Selective Layout Cutting**

### What it is

- Algorithmic Selective Cutting: Allegro<sup>®</sup> X and Allegro X Allegro Package Designer enhancements that enable the partitioning and stitching together of a layout design.

- Design will be cropped per user selected nets/margin, then translated.

- Reduces the <u>translation time</u> and accelerates the <u>SI/PI extraction setup and overall runtime</u> to get results.

- Creates module files that can be shared across different teams (layout designers, SI/PI engineers.

## **Algorithmic Selective Layout Cutting**

How it benefits design and simulation

- Traditional flow: In-design analysis (IDA) and Sigrity<sup>™</sup>/Clarity<sup>™</sup> extractions work by extracting the contents of Allegro<sup>®</sup> X PCB /Allegro X Advanced Package Designer databases to .spd format

- Translates entire design to .spd before trimming, leading to significant time (translation, simulation setup, runtime) and memory wasted

- New flow: before translating, generate a precut Allegro DB, including the objects needed

- Result is much smaller design, extremely fast

.spd file generation

- Bypass mode: Real-time design cut and margin preview prior to spd file generation

- Module mode: Real-time design cut, margin preview and module creation prior to spd file generation

JAN. 28–30, 2025

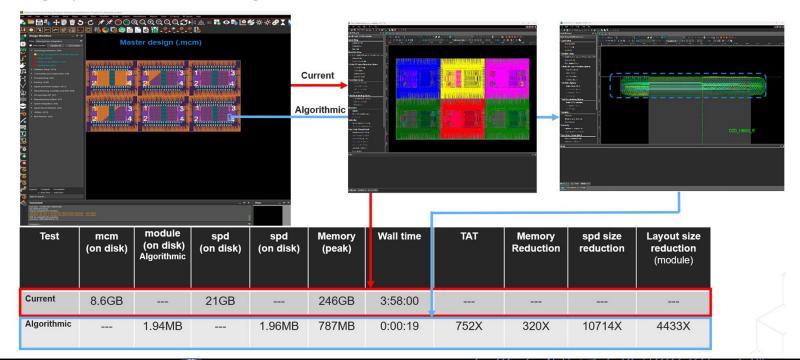

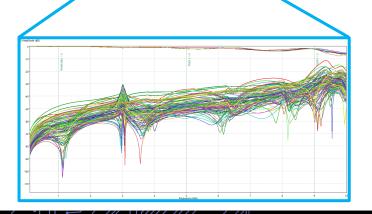

### Algorithmic Selective Layout Cutting Benchmarks

• D2D sample Impedance profile: 8 ASIC's, 24 HBME3s, 1100 IPD caps, 503000 design structures (PG, signal), 13.4M vias, 51,000 Pkg balls

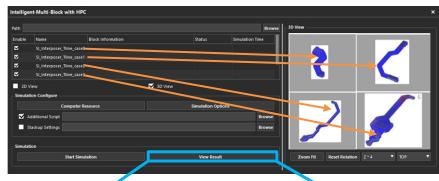

### Intelligent Multi-Block Extraction Motivation, What it is

- Clear need to better integrate the layout of interposers, IC packages, and PCBs to extraction and analysis engines

- More extractions needed earlier in the design cycle

- **<u>Translation</u>** and <u>runtime</u> are critical to accelerate analysis and optimizations

- Growing design complexity stressing translations, model preparation for extraction

- How to address this intelligently to feed our high-capacity solvers?

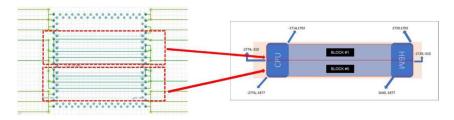

- Intelligent multi-block extraction

- Once a layout file is translated, smaller blocks can be created for rapid simulation

- Automatically <u>cut the simulation file into smaller</u> <u>blocks</u>, create ports and settings for each block, starts and monitors <u>simulations in parallel</u>

JAN. 28–30, 2025

## **Intelligent Multi-Block Extraction**

### How it benefits analysis

- Automatically <u>cut simulation file into</u> <u>smaller blocks</u>, create ports and settings for each block, starts and monitors <u>simulations</u> <u>in parallel</u>

- Thus, the overall turnaround time reduces for improvements in <u>translation</u> <u>time</u> and <u>runtime</u>

- Having consistent, reliable extractions is key to enabling data mining and analysis comparing design iterations, previous tapeouts, measurements correlations, etc.

- Establishes traceability and creates design references

JAN. 28–30, 2025

## **AI-Driven Design Synthesis with Constraints**

### Pre-layout analysis

#### Allegro<sup>®</sup> X/APD Constraint Manager

| File Edit Objects Calumin |            |         | ools Mindow Help                       |                              |            |       |           |            |                   |               |          |              | - 6 -     |

|---------------------------|------------|---------|----------------------------------------|------------------------------|------------|-------|-----------|------------|-------------------|---------------|----------|--------------|-----------|

| 0 0 5                     | × II •     | 0 0     | 8888 B 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 | 00                           | a *o *o *o | 2 🖫 🔍 |           |            |                   |               |          |              |           |

| ksheet Selector 🖉         | × ACCURACE |         |                                        |                              |            |       |           |            |                   |               |          |              |           |

|                           |            | Objects |                                        |                              | Line Width |       |           |            | Differential Pair |               |          |              |           |

|                           | Tree       |         | Name                                   | Referenced Physical<br>Clark |            |       | Min Width | Max Length | Min Line Specing  | Primary Gap   | Noth Gap | (+)Televance | Gillesnee |

| Physical Constraint Set   | .164       |         | run i                                  |                              |            |       |           |            |                   |               |          |              |           |

|                           |            |         |                                        |                              |            |       |           |            |                   |               |          |              |           |

| A Luyer                   | Date       |         | * ACCURATIVE                           |                              |            |       |           |            |                   |               |          |              |           |

|                           |            |         | <ul> <li>Intrast</li> </ul>            |                              |            |       |           |            |                   |               |          |              |           |

| a lat                     |            |         | <ul> <li>DOT INUS</li> </ul>           |                              |            |       |           |            |                   |               |          |              |           |

| Al Leyro                  |            |         | <ul> <li>RESPECTATIONS</li> </ul>      |                              |            |       |           |            |                   |               |          |              |           |

| Region                    |            |         | <ul> <li>IS CHM DP</li> </ul>          |                              |            |       |           |            |                   | £004308.005.8 |          |              |           |

|                           |            |         |                                        |                              |            |       |           |            |                   |               |          |              |           |

Allegro X/APD/Sigrity™ Aurora Design

# Sigrity Topology Workbench

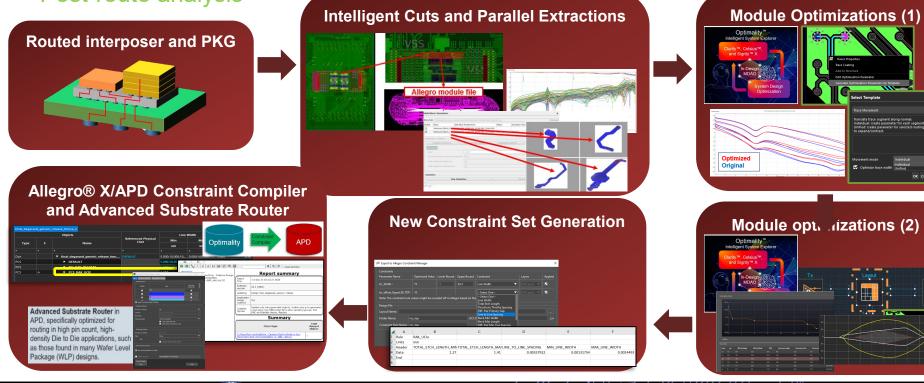

#### Allegro X/APD Constraint Compiler and Advanced Substrate Router

#### New Constraint Set Generation

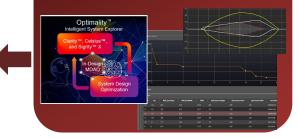

#### Optimality<sup>™</sup> Explorer

JAN. 28–30, 2025

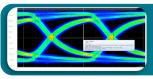

### System-Level SI Post-Route Optimization Methodology Post-route analysis

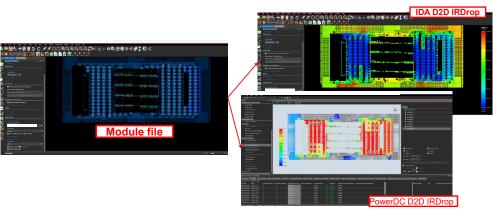

## **PDN Analysis**

### Die-to-die IR-drop example

- Layout-based cut preview quickly identifies "analysis area" prior to analysis launch

- Quick 3D viewing and PI fine tunning

- Optimized changes can be annotated back to main design

JAN. 28-30, 2025

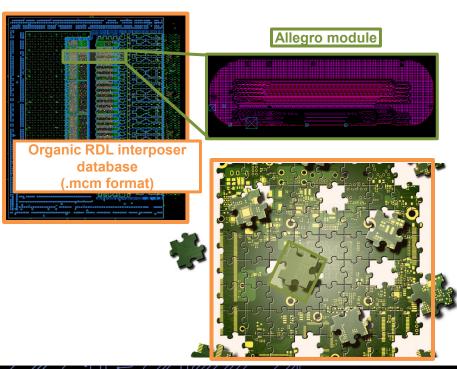

### Heterogeneous System Extractions Multi-fabric analysis of interposers, IC packages, and PCBs

#### Interposer/PKG Design Cropping

- Group Relevant Nets and Areas for SI/PI Analysis

- Define cutting regions and margin

- · Crop layout as desired with output .mcm, etc.

#### Translation of target analysis nets and area

- Translate already cropped GDS/MCM/SIP files

- Model cleanup and translation for SIPI Analysis

- Vastly reduced translation runtime and allows for easy sharing of IP blocks for SIPI analysis

#### Interposer/PKG Multi Block Analysis Automation

- Batch mode extraction of nets

- Define common ports, extraction setup

- Traceability: Consistent results and enables easy comparison to previous Tapeouts or design iterations

#### Verification of System Performance w/ Spectre

Channel analysis with SystemSI

Optimization/Monte Carlo/Statistical Analysis: via translations, decap placement, routing, etc.

#DesignCon

(informa markets

- · Reduce to smaller .spd files for deeper analysis and to reduce runtime

- Provide constraints and run in Optimality

- Pass back constraints to Layout Designers for review

## Conclusion

- High-performance computing chip designs challenging translators and layout tools

- Keys to success: <u>Parallelization</u>, integration, and <u>Turn-Around-Time (TAT)</u>

- Algorithmic Selective Cutting

- Enables partitioning and stitching together of layout design

- Reduce <u>translation time</u> and accelerate <u>SIPI extraction setup and</u> <u>overall runtime</u> to get results

- Rapid and efficient translation enables automation flows with Sigrity<sup>™</sup> and Clarity<sup>™</sup> solvers

- Edits made to module can be reapplied to original layout database

Intelligent Multi-Block Extraction

#DesignCon

- Automatically <u>cut simulation file</u> <u>into smaller blocks</u>, create ports and settings for each block, starts and monitors <u>simulations in</u> <u>parallel</u>

- Overall turnaround time is reduced

- Consistent, reliable extractions enable data mining and analysis

- Establishes traceability and creates design references

## **Conclusion and Next Steps**

- Algorithmic Selective Cutting and Intelligent Multi-Block extraction methodologies enable flows such as:

- Al-driven design synthesis with constraints

- System-level SI post-route optimization

- Multi-fabric analysis of interposers, IC packages and PCBs

- Provide your design teams with the ability to:

- Distribute layout and analysis efficiently within scalable workflows

- Integrate layout of interposers, IC packages and PCBs within simulation and analysis domain (multi-fabric analysis)

- Run more extractions needed and earlier in design cycle

- Algorithmic selective layout cutting methodology implemented in other layout tools

- Facilitates layout file stream out: directly exports .spd file (considering the cuts) instead of GDS, no need for supporting files (tech and map files)

# Thank you!

### **QUESTIONS?**

### **Pedro El-Awar**

Lead Application Engineer , Cadence Design Systems mattioli@cadence.com| www.cadence.com

#DesignCon

18

## **Conclusion and Next Steps**

- High-performance computing chip designs have been challenging translators and layout tools given the growing scale of engineering designs.

- Need to provide design teams the ability to:

- Distribute the layout and analysis efficiently within scalable workflows.

- Integrate the layout of interposers, IC packages and PCBs within the simulation and analysis domain (multi-fabric analysis)

- Run More extractions needed and earlier in the design cycle

- Parallelization, integration, and Turn-Around-Time (TAT) are key to success.

- Algorithmic Selective Cutting in Allegro and APD enables the partitioning and stitching together of a layout design (module-based approach). Reduces the translation time and accelerates the SIPI extraction setup and overall runtime to get results.

- Rapid and efficient translation enables automation flows with Sigrity<sup>™</sup> and Clarity<sup>™</sup> solvers.

- Edits are made to the module can be reapplied to the master layout database

- Intelligent Multi-Block extraction

- Automatically cut the simulation file into smaller blocks, create ports and settings for each block, starts and monitors simulations in parallel

- Overall turnaround time is reduced for the improvements in the translation time and runtime

- Consistent, reliable extractions enable data mining and analysis comparing design iterations, measurements correlations. Establishes traceability and creates design references.

# **Conclusion and Next Steps**

- Algorithmic Selective Cutting and Intelligent Multi-Block extraction methodologies enable flows such as:

- AI-Driven Design Synthesis with Constraints

- System-Level SI Post-Route Optimization

- Multi-fabric analysis of interposers, IC packages and PCBs

- Algorithmic selective layout cutting methodology to be implemented in other layout tools (<u>Innovus™</u> <u>Implementation System</u>)

- Facilitates the layout file stream out: directly exports .spd file (considering the cuts) instead of GDS, no need for supporting files (tech and map files).